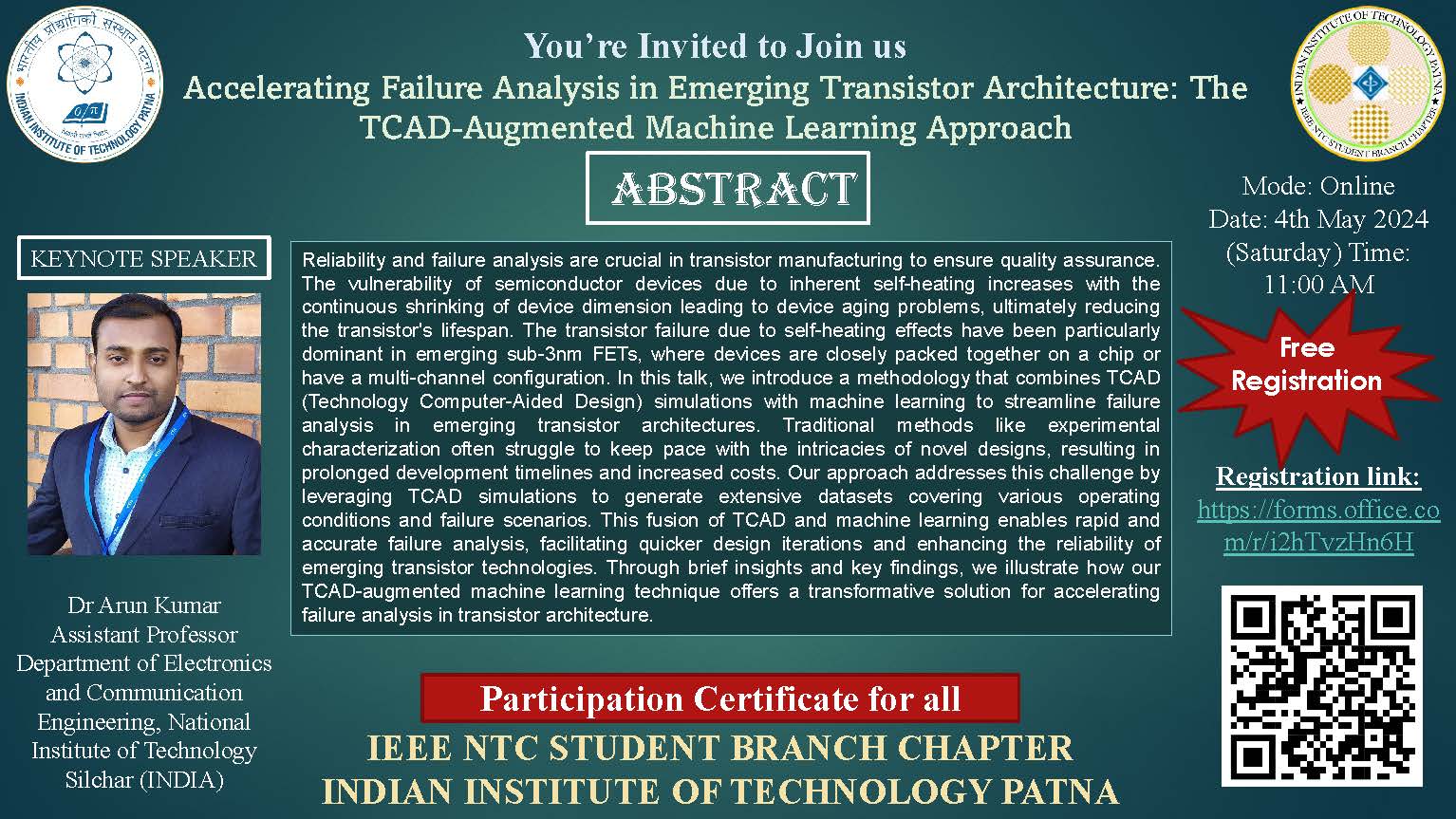

Accelerating Failure Analysis in Emerging Transistor Architecture: The TCAD-Augmented Machine Learning Approach

Reliability and failure analysis are crucial in transistor manufacturing to ensure quality assurance. The vulnerability of semiconductor devices due to inherent self-heating increases with the continuous shrinking of device dimension, leading to device aging problems and ultimately reducing the transistor's lifespan. The transistor failure due to self-heating effects has been particularly dominant in emerging sub-3nm FETs, where devices are closely packed together on a chip or have a multi-channel configuration. In this talk, we introduce a methodology that combines TCAD (Technology Computer-Aided Design) simulations with machine learning to streamline failure analysis in emerging transistor architectures. Traditional methods like experimental characterization often struggle to keep pace with the intricacies of novel designs, resulting in prolonged development timelines and increased costs. Our approach addresses this challenge by leveraging TCAD simulations to generate extensive datasets covering various operating conditions and failure scenarios. This fusion of TCAD and machine learning enables rapid and accurate failure analysis, facilitating quicker design iterations and enhancing the reliability of emerging transistor technologies. Through brief insights and key findings, we illustrate how our TCAD-augmented machine-learning technique offers a transformative solution for accelerating failure analysis in transistor architecture.

Date and Time

Location

Hosts

Registration

- Date: 04 May 2024

- Time: 11:00 AM to 12:00 PM

- All times are (UTC+05:30) Chennai

-

Add Event to Calendar

Add Event to Calendar

- Starts 29 April 2024 12:00 AM

- Ends 03 May 2024 12:00 AM

- All times are (UTC+05:30) Chennai

- No Admission Charge

Speakers

Dr Arun Kumar of NIT Silchar

Accelerating Failure Analysis in Emerging Transistor Architecture: The TCAD-Augmented Machine Learning Approach

Biography:

Dr Arun Kumar has been working as an Assistant Professor in the ECE Department at the National Institute of Technology, Silchar, since July 2022. He earned his Ph.D. degree in Microelectronics from IIT Patna, India, in 2020. Before joining NIT Silchar, Dr. Arun worked as an Assistant Professor in the ECE Department at TIET, Patiala, India. He is a member of IEEE, IEEE Electron Device Society and IEEE TechEthics Community. Dr. Arun has been awarded junior and senior research fellowships by CSIR, Government of India, in 2016 and 2018, respectively. Dr Arun received a Foreign Travel Grant from CSIR and an International Travel Grant from SERB, Government of India. He has contributed significantly to the field of microelectronics, with several research papers published in reputable journals and presentations of his work at flagship IEEE conferences both in India and abroad.

Email:

Address:NIT Silchar, , Silchar, India

Media

| screenshot | 683.28 KiB | |

| flyer | 249.92 KiB |