CMOS VLSI Design Challenges and Opportunities: An Industry Perspective

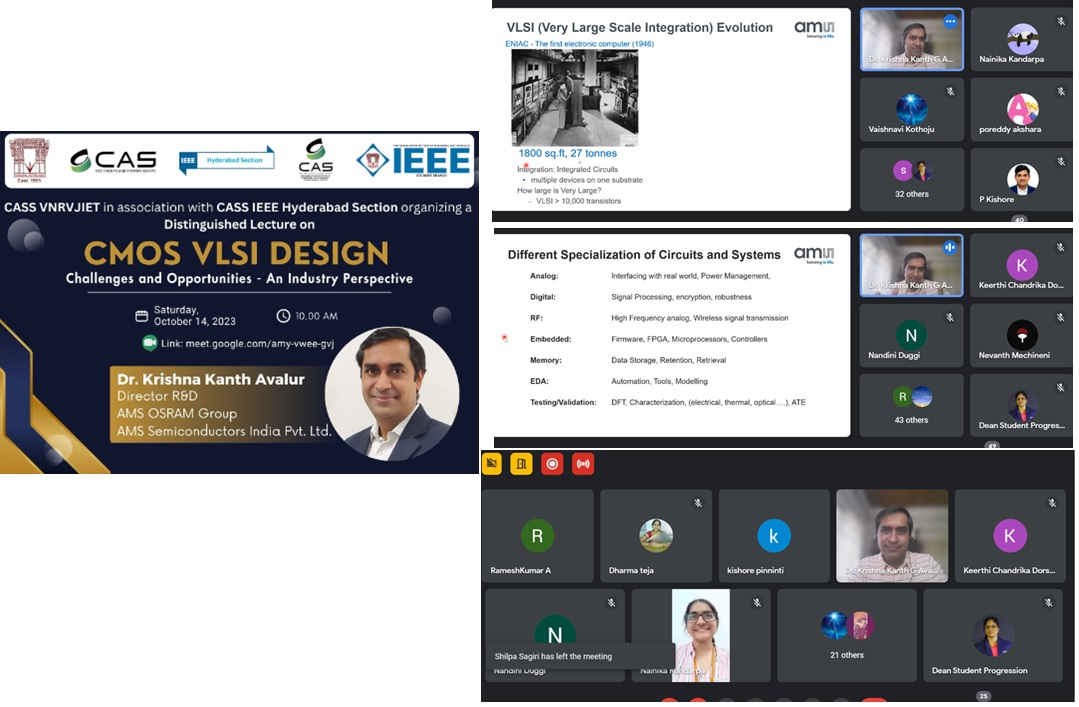

CASS VNRVJIET (SBC60651A) in association with CAS/EDS Chapter of IEEE Hyderabad section is organizing a Distinguished Lecture on

CMOS VLSI Design Challenges and Opportunities: An Industry Perspective

Saturday, 14-October-2023, 10:00 AM (Webinar)

Link: meet.google.com/amy-

Speaker: Dr. Krishna Kanth Avalur, Director R&D, ams OSRAM, Hyderabad

Date and Time

Location

Hosts

Registration

-

Add Event to Calendar

Add Event to Calendar

- Contact Event Hosts

-

CASS VNRVJIET (SBC60651A)

- Co-sponsored by CASS VNRVJIET (SBC60651A)

Speakers

Dr. A. G. Krishna Kanth of ams OSRAM

Dr. A. G. Krishna Kanth of ams OSRAM

CMOS VLSI Design Challenges and Opportunities: An Industry Perspective

Greetings !

Chips will continue to shrink , ofcourse. We, along with other semiconductor companies, are continuing to push towards the next goal of high-performance cost-effective semiconductor technologies. The ability to do high performance analog designs in lower technology nodes primarily for digital shrink of transistors is a challenges that VLSI designers face. This is an introductory talk which woudl explain about history of VLSI circuits, different specializations for researchers working in the field of circuits and systems, key design and manufacturing challenges followed by some real-life application examples on how VLSI helps in building state-of-the-art miniatured circuits and systems.

IEEE VNRVJIET SB in association with IEEE VNRVJIET SB CAS Student Chapter is organizing a distinguished lecture on "CMOS VLSI Design: Challenges and Opportunities - An industry perspective"

Biography:

Speaker: Dr. A .G .Krishna Kanth is currently the Director of Analog Mixed-Signal R&D at AMS OSRAM group. He is an IEEE Senior member and currently the Vice-Chair for IEEE CAS/EDS Hyderabad Chapter and is frequently involved in delivering technical lectures at various Universities. He received his PhD from IIIT Hyderabad. He finished his B.Tech and M. Tech from IIT Bombay with Specialization in Microelectronics. He was awarded President of India Shankar Dayal Sharma gold medal and IIT Bombay Student Roll of Honour in 2002. Analog IC Design is his passion and his specialization includes sensors and sensor interfaces, high performance analog signal processing, power management for automotive and consumer semiconductor IC design. He worked earlier with Texas Instruments Bangalore and Qualcore Logic Hyderabad leading the Analog IC design teams. He is an adjunct professor at IIT Hyderabad and Digital University Kerala. He is on academic council and BoS member at several universities. He has 12 patents and 10 IEEE publications. He is one of the designated AE for TCAS-II for 2024 & 2025.

Email:

Address:Hyderabad, India, 500081

Agenda

Chips will continue to shrink , ofcourse. We, along with other semiconductor companies, are continuing to push towards the next goal of high-performance cost-effective semiconductor technologies. The ability to do high performance analog designs in lower technology nodes primarily for digital shrink of transistors is a challenges that VLSI designers face. This is an introductory talk which woudl explain about history of VLSI circuits, different specializations for researchers working in the field of circuits and systems, key design and manufacturing challenges followed by some real-life application examples on how VLSI helps in building state-of-the-art miniatured circuits and systems.

IEEE VNRVJIET SB in association with IEEE VNRVJIET SB CAS Student Chapter is organizing a distinguished lecture on "CMOS VLSI Design: Challenges and Opportunities - An industry perspective"