Escuela de Invierno en Dispositivos Semiconductores y Circuitos Integrados

IEEE-EDS - First Mexico Technical Meeting 2025 (MTM_1-2025)

EDS Mexico Chapter and Cinvestav-IPN Student Branch Chapter

Centro de Nanociencias y Micro y Nanotecnologías IPN

EVENTO SIN COSTO

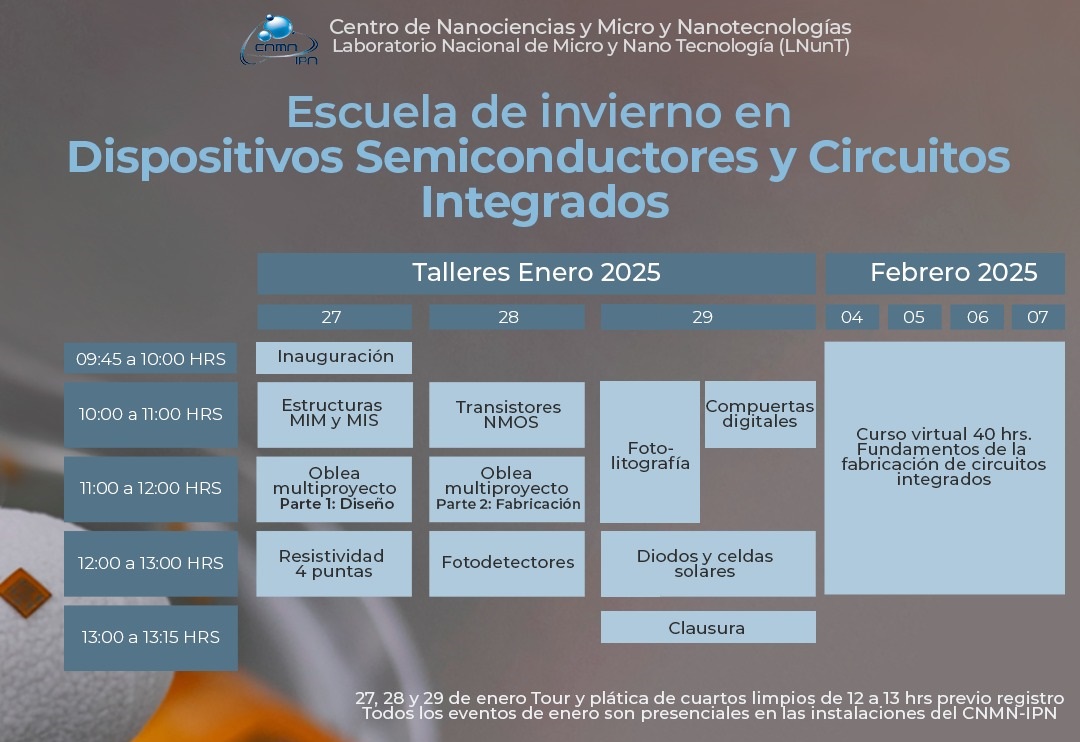

El Laboratorio Nacional de Micro y Nano Tecnología (LNunT), te invita a la Escuela de Invierno en Dispositivos Semiconductores y Circuitos Integrados del 27 de enero al 07 de febrero de 2025, dirigida a profesores y estudiantes de los niveles: medio superior, superior y posgrado.

Objetivo: Brindar conocimientos teóricos y prácticos para conocer y aprovechar las capacidades del Laboratorio Nacional de Micro y Nanotecnología (LNunT) sede Instituto Politécnico Nacional (IPN).

Actividades:

-Talleres presenciales -Cursos virtuales -Tours de cuartos limpios -Realidad virtual de cuartos limpios

Da clic en la imagen para realizar el registro en las actividades que desees participar:

|

|

|

|

|

|

|

|

|

| Evento sin registro: |  |

Del 04 al 07 de febrero podrás tomar el curso virtual “Fundamentos de la Fabricación de Circuitos Integrados”. En donde conocerás los procesos para fabricar transistores CMOS a base de silicio y herramientas de simulación tecnológica y entrenamiento virtual.

La asistencia a cada taller será acredora de una constancia de participación.

EVENTO SIN COSTO

Comité organizador

Dr. Oscar Camacho Nieto,

Director CNMN-IPN ocamacho@ipn.mx

Dr. Cuauhtémoc León Puertos,

Subdirector de Micro y Nanotecnologías CNMN-IPN cleon@ipn.mx

Dr. Norberto Hernández Como,

Director de Escuela de Invierno nohernandezc@ipn.mx

Dr. Isai S Hernandez Luna,

Advisor IEEE EDS Cinvestav-IPN Student Branch hdezisai@gmail.com

Dr. Ivan Garduño Vertiz

Chair EDS IEEE Mexico sgarduno@cinvestav.mx

Date and Time

Location

Hosts

Registration

-

Add Event to Calendar

Add Event to Calendar

- Av. Luis Enrique Erro S/N, Unidad Profesional Adolfo López Mateos, Zacatenco, Alcaldía Gustavo A Madero

- Ciudad de México

- Ciudad de México, Distrito Federal

- Mexico 07738

- Building: Instalaciones del CNMN-IPN y Lab ME - Laboratorio de Mediciones Eléctricas

- Click here for Map

- Contact Event Hosts

-

Contacto de Centro de Nanociencias y Micro y Nanotecnologías del IPN

Dr. Cuauhtémoc León Puertos cleon@ipn.mx Teléfono: (55)57296000 Ext. 57522

Subdirector de Micro y Nanotecnologías del CNMN-IPN

- Co-sponsored by Centro de Nanociencias y Micro y Nanotecnologías del IPN

Speakers

Dr. Norberto Hernandez Como of CNMN-IPN

Taller Oblea Multiproyecto

Se realizará un ejemplo de como trabajamos en proyectos multi-oblea útiles para ahorrar costos en la fabricación de dispositivos semiconductores y/o circuitos integrados. En la parte de diseño, cada participante utilizará software especializado para diseñar una geometría simple (un logo, líneas o motivos geométricos). En la parte de fabricación, se depositará un metal sobre un sustrato flexible y se grabará el diseño realizado en la primera parte mediante fotolitografía (depósito de resina, exposición, revelado, ataque químico y limpieza). Finalmente, lo fabricado se cortará individualmente. Todo este proceso podrá ser visto en vivo durante el taller.

Día: 27 y 28 de Enero del 2025

Hora: 11:00 a 12:00

Número de participantes: 30

Lugar: Lobby de Cuartos Limpios - CNMN

Email:

Dr. Isai S Hernandez Luna of CNMN-IPN

Taller Estructuras MIM/MIS

Descripción: mostrar como se realizan mediciones I-V y C-V a estructuras MIM (metal-insulator-metal) y MIS (metal-insulator-semiconductor) y su respectiva extracción de parámetros eléctricos.

Día: 27 de Enero del 2025

Hora: 10:00 a 11:00

Número de participantes: 15

Lugar: Laboratorio de Mediciones Eléctricas - CNMN

Email:

Ing. Hamlet Jorge Marmolejo Martínez y Ing. Rodrigo Vázquez Cruz of UPIITA-IPN

Demostracion cuarto limpio en realidad virtual

Implementación de una plataforma de entrenamiento en un ambiente virtual, la cual consiste en un cuarto limpio enfocado a la fabricación de semiconductores.

Día: 27, 28 y 29 de Enero del 2025

Hora: 10:00 a 13:00

Número de participantes: abierto

Lugar: Lobby de Cuartos Limpios - CNMN

Email:

Dra. Haydeé González, Dr. Norberto Hernandez of CNMN-IPN

Tour cuarto limpio y plática sobre LNunT

En este tour conocerás sobre la infraestructura dentro de los cuartos limpios del CNMN-IPN. También aprenderás sobre las características de los cuartos limpios y porque son importantes para el desarrollo de dispositivos semiconductores y circuitos integrados.

Día: 27,28 y 29 de Enero de 2025

Hora: 12:00 a 13:00 Horas.

Número de participantes: 20

Lugar: Cuartos limpios.

Email:

M.C. Leonardo Sebastian Sanchez Fernandez of CNMN-IPN

Taller: Resistividad 4-puntas

Mostrar los alcances y limitaciones de la técnica de 4-puntas para medir la resistencia de hoja (sheet resistance) de películas conductoras y semiconductoras depositadas por técnicas como: sputtering y evaporación por haz de electrones. Se mostrará como se calcula la resistividad eléctrica de los materiales.

Día: 27 de Enero del 2025

Hora: 12:00 a 13:00

Número de participantes: 15

Lugar: Laboratorio de Mediciones Eléctricas - CNMN

Email:

M.C. Abril Abilene Garcia Soriano of CNMN-IPN

Taller transistores NMOS

Mostrar como se realizan mediciones I-V de transistores de película delgada para obtener sus curvas transferenciales en regímenes lineal y saturación, y sus curvas de salida. También se presentan como se extraen sus parámetros eléctricos como voltaje de umbral y movilidad.

Día: 28 de Enero del 2025

Hora: 10:00 a 11:00

Número de participantes: 15

Lugar: Laboratorio de Mediciones Eléctricas - CNMN

Email:

Ing. Nicol Alejandra Munguía Fernández of UABC

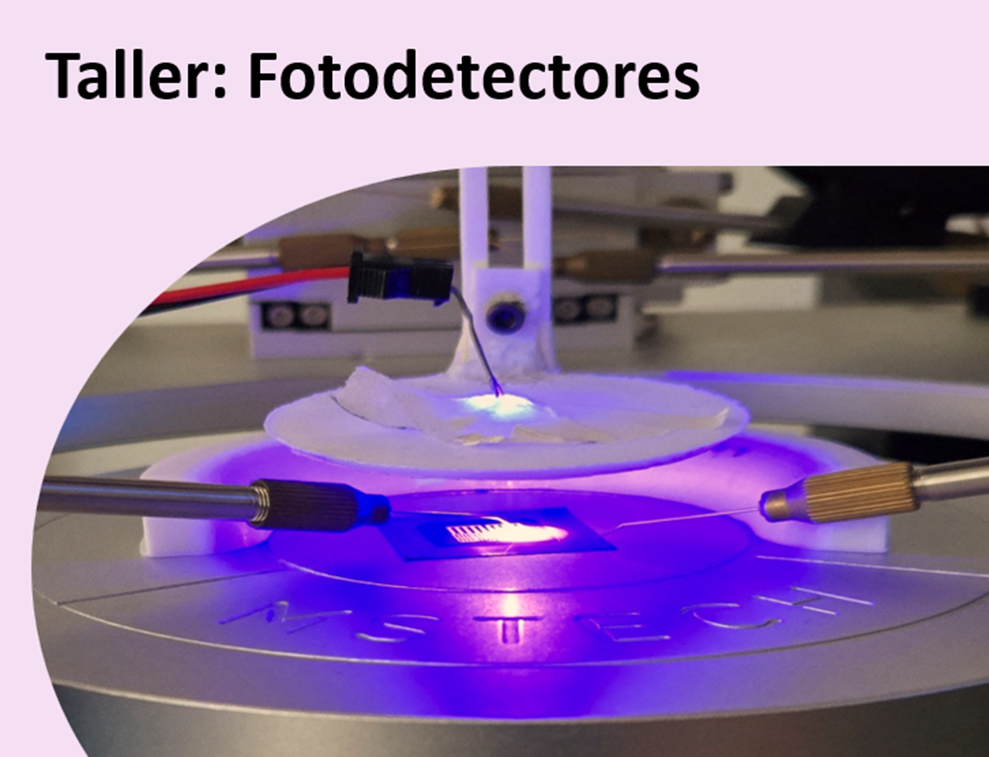

Taller fotodetectores

Se mostrará el procedimiento para obtener curvas I-V de fotodetectores tales como fotorresistencias y fotodiodos bajo la incidencia de diferentes longitudes de onda. Además, se presentará el caso de su operación en función del tiempo. Finalmente, se describirá el método para la extracción de parámetros clave.

Día: 28 de Enero del 2025

Hora: 12:00 a 13:00 pm

Número de participantes: 15

Lugar: Laboratorio de Mediciones Eléctricas - CNMN

Email:

Dr. Jacobo Esteban Munguia Cervantes y Dr. Mario Francisco Ávila Meza of CNMN-IPN

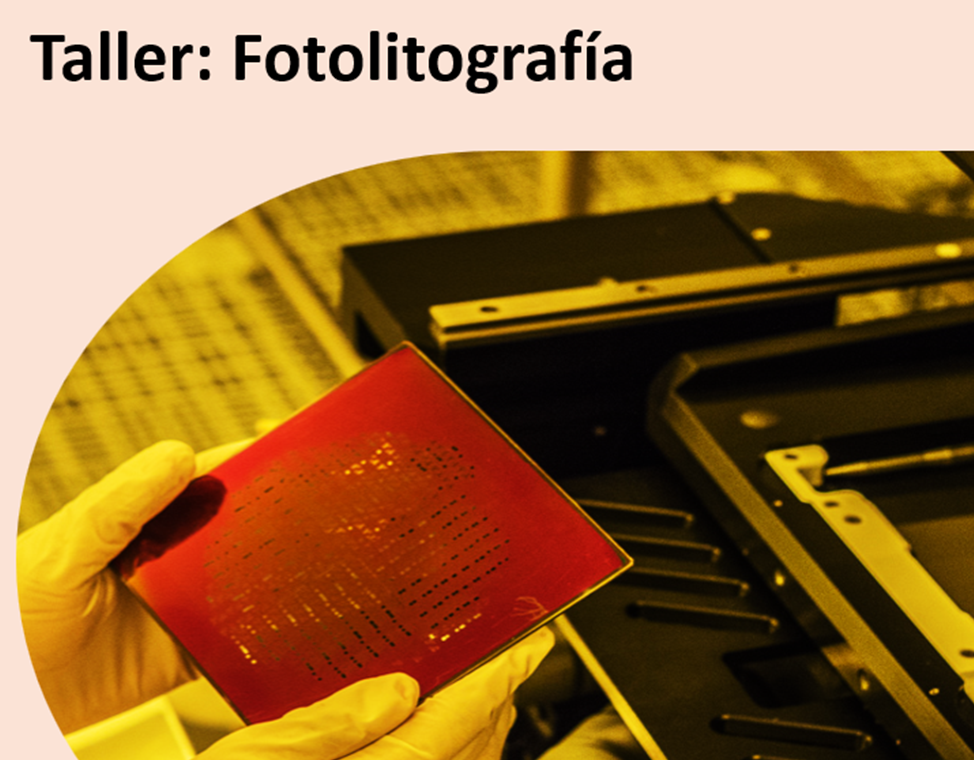

Taller Fotolitografía

Se demostrará el principio de funcionamiento de la técnica de fotolitografía mediante el uso de substratos y fotomascaras empleados para la trasferencia de patrones micrométricos. De igual manera, se mostrarán los diferentes procesos que se pueden realizar con el equipo de fotolitografía que se encuentra dentro del cuarto limpio del laboratorio de Micro y Nanotecnologías.

Día: 29 de Enero del 2025

Hora: 10:00 a 12:00

Número de participantes: 10

Lugar: Cuartos Limpios - CNMN

Email:

Dr. Arturo Torres Sánchez of CNMN-IPN

Taller Compuertas Digitales

Demostración práctica de la medición de compuertas digitales fabricadas con transistores de película delgada (TFT) NMOS. Se explicará el proceso de caracterización y se presentarán las curvas de los circuitos básicos: inversor, compuerta NAND y compuerta NOR."

Día: 29 de Enero del 2025

Hora: 10:00 a 11:00

Número de participantes: 15

Lugar: Laboratorio de Mediciones Eléctricas - CNMN

Email:

Ing. Nicol Munguía y M.C. Leonardo Sanchez of CNMN-IPN

Taller Diodos y Celdas Solares

Se mostrará el procedimiento para realizar mediciones I-V y C-V a diodos de tipo homounión, heterounión y/o Schottky. Además, se presentará el caso para celdas solares. Finalmente, se extraerán los parámetros clave para cada dispositivo

Día: 29 de Enero del 2025

Hora: 12:00 a 13:00

Número de participantes: 15

Lugar: Laboratorio de Mediciones Eléctricas - CNMN

Email:

Dr. Norberto Hernandez Como of CNMN-IPN

Curso: Fundamentos de la fabricación de circuitos integrados

El participante obtendrá los conocimientos necesarios para entender las técnicas y procesos de fabricación más relevantes utilizados en el desarrollo de los dispositivos semiconductores y circuitos integrados. Se brindarán los conocimientos teóricos en cuanto a: dopaje, ataque, depósito, fotolitografía, y un proceso de fabricación CMOS de 28nm y se utilizarán herramientas digitales como la simulación tecnológica y prácticas en un cuarto limpio virtual.

Día: 4, 5, 6 y 7 de Febrero del 2025

Hora: 9:00 a 13:00

Número de participantes: 50

Lugar: Virtual a través de TEAMS

Email:

Agenda