Utilizing Electrical Test Methods for Thermal Measurement, Reliability and Quality Assessment

Utilizing Electrical Test Methods for Thermal Measurement, Reliability and Quality Assessment

We continue our sequence of in-depth tech events for the year with a talk on test methods for electronic devices

From multi-core chips in slim smartphone devices or compact packaging of power semiconductor modules for lightweight electric vehicle inverters, understanding semiconductor package heat dissipation remains important for performance and product reliability purposes.

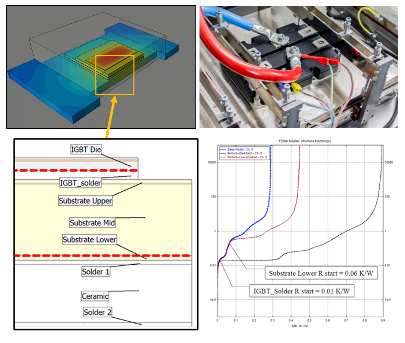

This presentation introduces electrical test methods covered by JEDEC 51-1 standards. By utilizing this approach, the difficulties and problems measuring temperature at the component’s die are overcome. Further use of the techniques allow transient thermal response measurement, for package and system thermal characterization, which can be applied to identifying thermal degradation, verifying package material quality for manufacturing purposes, and supporting thermal design processes by generating validated semiconductor package thermal models. This method is an alternative to XRay, CSAM or destructive inspection methods for certain failure diagnosis applications.

Key topics:

- Electrical test methods for thermal measurement, JEDEC 51-1 series, transient thermal response & structure functions

- Package material structure object mapping

- Power Electronics – IGBT thermal degradation identification & power cycling studies

- Package Material Defect Identification

- Recent IP developments in detailed thermal model calibration

Following this there will a general discussion, Q&A and update on the current state of landscape (recent major annoucenments will be also shared)

Date and Time

Location

Hosts

Registration

-

Add Event to Calendar

Add Event to Calendar

- 115 Library Drive

- Oakland University

- Rochester, Michigan

- United States 48309-4479

- Building: Engineering Center

- Room Number: EC 254

- Click here for Map

- Contact Event Host

-

ganesan@oakland.edu

An event flyer is available at this link -> March 2018 03 Event Flyer

- Co-sponsored by Prof. Subramaniam Ganesan & Education Society SE Michigan chapter

- Starts 05 March 2018 02:22 PM UTC

- Ends 30 March 2018 01:22 AM UTC

- No Admission Charge

- Menu: Vegetarian Pizza, Cheese Pizza, Regular Soda Pop, Diet Soda Pop

Speakers

Joe Proulx of Mentor Graphics

Joe Proulx of Mentor Graphics

Utilizing Electrical Test Methods for Thermal Measurement, Reliability and Quality Assessment

From multi-core chips in slim smartphone devices or compact packaging of power semiconductor modules for lightweight electric vehicle inverters, understanding semiconductor package heat dissipation remains important for performance and product reliability purposes.

This presentation introduces electrical test methods covered by JEDEC 51-1 standards. By utilizing this approach, the difficulties and problems measuring temperature at the component’s die are overcome. Further use of the techniques allow transient thermal response measurement, for package and system thermal characterization, which can be applied to identifying thermal degradation, verifying package material quality for manufacturing purposes, and supporting thermal design processes by generating validated semiconductor package thermal models. This method is an alternative to XRay, CSAM or destructive inspection methods for certain failure diagnosis applications.

Biography:

Joe Proulx is a Senior Application Engineer for Mentor Graphics Corporation since 2005, specializing in thermal design and supporting product reliability testing. Joe Proulx over 20 + years of experience as thermal engineer in industry including companies such as Sycamore Networks. He has extensive computational fluid dynamics (CFD) experience for electronics cooling analysis, and more than 7+ years specializing in test measurement for thermal characterization of semiconductors and reliability assessment. Joe has several patents pending in package thermal modeling and validation subjects. He also regularly contributes to IEEE & SAE conference papers for power electronics reliability and electronics thermal simulation subjects.

Address:United States

Agenda

6:00 PM - Welcome and Introductions, Chapter business update, Pizza

6:15 PM - Main Presentation: Utilizing Electrical Test Methods for Thermal Measurement, Reliability and Quality Assessment

7:30 PM - Post event discussion, Q&A and landscape update

7:45 PM - Wrap Up

7:45 to 8 PM - Networking

Professional Development Hours/Units (PDU/PDH) are available for this talk, but must be requested in advance!

A Joint Oakland University/IEEE Computer Society/Education Chapter Presentation, open to all