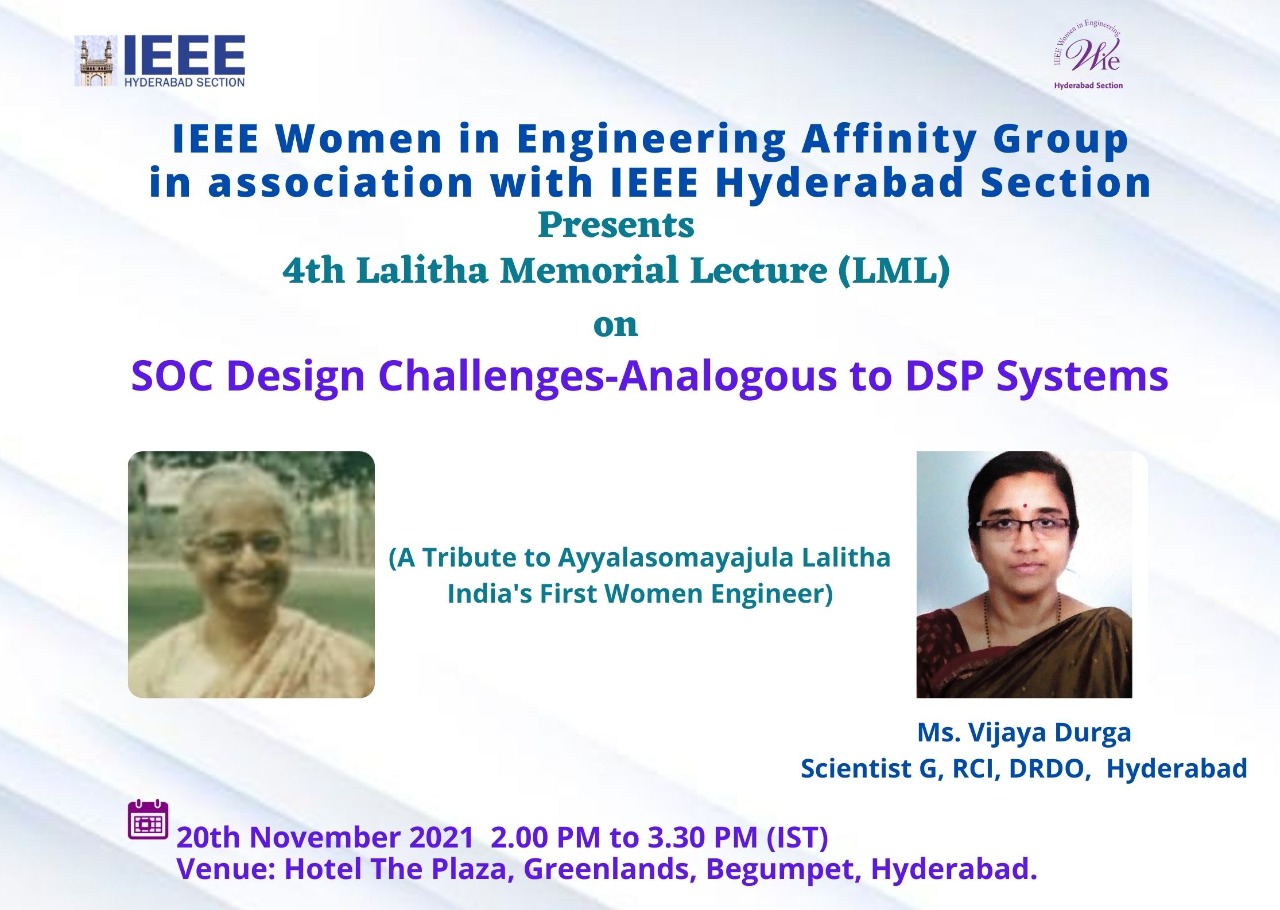

IEEE WIE AG in association with IEEE-Hyderabad Section/Fourth Flagship event Lalitha Memorial Lecture (LML) on "SOC Design Challenges- Analogous to DSP Systems" on 20th November, 2021 from 2.00 PM to 3.30 PM (IST)

IEEE WIE AG in association with IEEE-Hyderabad Section, India presents "2021 FOURTH FLAGSHIP LALITHA MEMORIAL LECTURE (LML)" ON 20-NOV-2021 from 2.00 PM to 3.30 PM (IST)

About Ayyalasomayajula Lalitha:

Ayyalasomayajula Lalitha was India's first Woman Engineer, graduated in 1943 in Electrical Engineering. She was born on 27 August 1919 in Chennai. She joined the Central Standards Organization in Shimla for a brief period.

She joined Associated Electrical Industries and started designing transmission lines, substation layout and executed various contracts. She was associated with the work on electrical generators for the Bhakra Nangal Dam. In 1953, the Council of the Institution of Electrical Engineers (IEE), London elected her to be an associate member and in 1966 to a full member. She was the only woman engineer from India to attend the First International Conference of Women Engineers and Scientists (ICWES) in New York in June 1964. She was an active volunteer in an international women engineering organization throughout her life. Lalitha’s life is a beacon of light for all the women who came after her in the 1950s to till date and her accomplishments inspire every woman.

Brief Details about Lalitha Memorial Lecture (LML)

IEEE-Hyderabad Section and WIE AG jointly conducts every year a Lalitha Memorial Lecture. This is a Flagship event of our Section and IEEE Hyderabad Section Women in Engineering Affinity Group. Distinguished/ eminent women who contributed to innovations, applications of technology for the advancement of our society, are invited by us for our LML for delivering lectures to enrich the knowledge of fellow professional engineers and students.

Brief Profile of the Invited Speaker:

Ms. Vijaya Durga, is working as Scientist-G at RCI, DRDO, Hyderabad. She is Leading the team for ASICs and SoC (System on Chip) designs at RCI for sister labs NPOL, NSTL, & ASL etc. From the specifications to design realization with team, testing, fabrication with industry, prototype board development and proving the functionality and design of embedded systems for different applications are the goals. She was also team member for first Indian chip ANUCO floating point co-processor in 1993. She has carried Architecture Design & development of DRDO first DRDO indigenous ASIC-ANUCO & fabricated successfully in 1993 as team member at ANURAG. Her team received Indian Patent. She has also carried Design & simulations of ANUPAMA 32-bit indigenous processor in 1995 as a team member, chip fabricated and tested successfully. She received Lab Level Team award from DRDO for first indigenous processor ANUPAMA in the year 1996. She was involved in design of DPRAM based DDS Frequency Synthesisers completed & fabricated with Indian fab at SITAR in 1997. These chips are widely used in the SONAR systems for under water applications. Received Lab level Scientist of the year award in 2000. As a Head of SOC wing at ANURAG, design & development of System on Chips based on DSP cores and designing ASICs, is leading a team of VLSI scientists for these activities and developed applications on to various SOCs/ASICs. She developed application boards, for ASICs/SOCs. These ASICs were subsequently used in production systems by BEL, BDL, ECIL & L&T.Chips were designed from the various requirements given by CAIR, DEAL , NSTL & NPOL. DSP cores designed are 16-bit and 32-bit and CEVA processor integration. Many of the ASICs fabricated at Indian fab using 1u technology at SITART are used in production systems. She also received Team lead award in yr 2007 at ANURAG. She is System Administrator for VLSI design & enhanced EDA set-up at ANURAG. She received DRDO Scientist of the year award from RM in the year 2010, for usage of various indigenous ASICs in End systems. She is Fellow of IETE, Member of IMAP Society. She has published many papers in national and international conferences and journals.

Registration and Joining Link: https://bit.ly/LML-2021

Date and Time

Location

Hosts

Registration

-

Add Event to Calendar

Add Event to Calendar

- Contact Event Hosts

-

- Dr. Y.Padma Sai, Chair, WIE AG- padmasai_y@ieee.org

- Dr.Harivardhagini Subhadra,Vice-Chair, WIE AG- harivardhagini@gmail.com

- Ms.Sangeeta Singh, Secretary,WIE AG - sangeeta.singh@ieee.org

- Co-sponsored by Mr. Srinivas Jasti, Chair, IEEE-Hyderabad Section

Speakers

Ms. Vijaya Durga

Fourth Flagship Lalitha Memorial Lecture (LML) on “SOC Design Challenges- Analogous to DSP Systems”

Performance of conventional DSP processors is typically sufficient only to manage low-rate, low-mobility systems. Even for moderate data rates or mobility requirement (more than a few hundred Kbit), high-end processors using VLIW/SIMD technologies operating at GHz are required. These processors are too expensive in terms of size, number of pins and power consuming. Design of optimum architecture for DSP & Programmable Baseband Processors(BPs), which operates on higher Bandwidth data, with optimum execution units and low control overhead, is one solution for increasing the performance with the same power. Complex operations like FFT, FIR Filters, OFDM, Correlations, Error correction algorithms for communication etc deals with vector operations to be performed on BPs with DSP support. DSPs like CEVA XC323 IP Core, TMS320C62X SOC also extended support for image/Video acceleration & for Neural Network processing etc. DSP Parameters that require customized repetitive operations modelling onto ASICs/SOCs with configurable accelerators helped for power, area & reduced interfaces rather than lengthy software execution time implementation. When it comes to customization of DSP tasks, it also needs to be evaluated with FPGA implementations and trade of re-configuration Vs life time of the product also to be considered.

SOC design for DSP algorithms keeping above requirements for on board applications and for battery operated communication devices is always challenging in view of miniaturization, power , frequency requirement and with minimal interfaces. What are the challenges faced from algorithm to chip testing and how solutions arrived will be presented with few case analysis. Mainly concentrating applications like Radar, SONAR etc.

Teams managing in the high attrition scenarios in the area of VLSI design until the end product tested, needs huge support and is always challenging

Agenda

1. Welcome address by Dr. Y. Padma Sai, Chair, IEEE WIE AG, Hyderabad Section

2. Address by Mr. Srinivas Jasti, Chair, IEEE Hyderabad Section

3. Talk by Ms. Vijaya Durga, Scientist-G, RCI, DRDO, Hyderabad

4. Vote of Thanks

More details about IEEE-Hyderabad Section are at www.ieeehyd.org

We invite Industry Professionals, Young Professionals, Faculty members ,Research Scholars and Students.