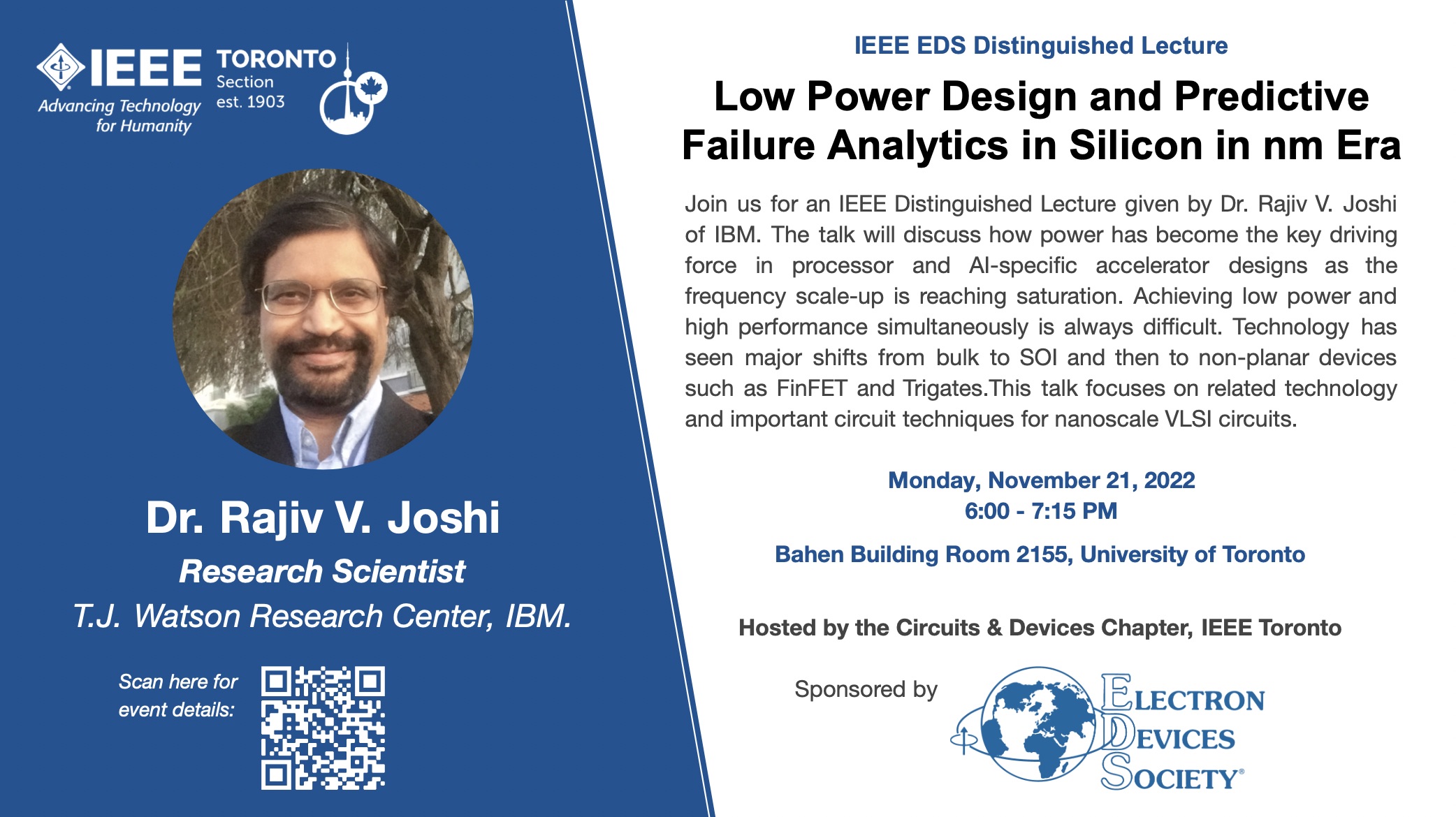

IEEE EDS Distinguished Lecture: Low Power Design and Predictive Failure Analytics in Silicon in nm Era

IEEE EDS Toronto is proud to invite you to a Distinguished Lecture by Dr. Rajiv V. Joshi of the T. J. Watson Research Center, IBM.

Join us Monday, Nov 21 at 6:00PM in BA 2155 on the University of Toronto main campus. Food and refreshments will be served.

Abstract

Power has become the key driving force in processor as well AI specific accelerator designs as the frequency scale-up is reaching saturation. In order to achieve low power system, circuit and technology co-design is essential. This talk focuses on related technology and important circuit techniques for nanoscale VLSI circuits. Achieving low power and high performance simultaneously is always difficult. Technology has seen major shifts from bulk to SOI and then to non-planar devices such as FinFET and Trigates.

This talk consists of pros and cons analysis on technology from power perspective and various techniques to exploit lower power. As the technology pushes towards sub-7nm era, process variability and geometric variation in devices can cause variation in power. The reliability also plays an important role in the power-performance envelope. This talk also reviews the methodology to capture such effects and describes all the power components. All the key areas of low power optimization such as reduction in active power, leakage power, short circuit power and collision power are covered. Usage of clock gating, power gating, longer channel, multi-Vt design, stacking, header-footer device techniques and other methods are described for logic and memory used for processors and AI. Finally the talk summarizes key challenges in achieving low power.

In addition the tutorial gives a brief overview of predictive failure analytics used in nm Technology. Process and environmental variations impact circuit behavior it is important to model their effects to build robust circuits. The tutorial describe how key statistical techniques can be effectively used to analyze and build robust circuits.

Date and Time

Location

Hosts

Registration

-

Add Event to Calendar

Add Event to Calendar

Loading virtual attendance info...

- 40 St George St

- Toronto, Ontario

- Canada M5S 2E4

- Building: Bahen Centre for Information Technology

- Room Number: BA2155

- Click here for Map

Speakers

Dr. Rajiv Joshi of IBM, T. J. Watson Research Center

Biography:

Dr. Rajiv V. Joshi is an IEEE Fellow, winner of the prestigious IEEE Daniel Noble award, and a key technical lead/Research Scientist at T. J. Watson research center, IBM. He received his B.Tech IIT (Bombay, India), M.S (MIT), and Dr. Eng. Sc. (Columbia University). He has led successfully predictive failure analytic techniques for yield prediction and also the technologydriven SRAM at IBM Server Group. His statistical techniques are tailored for machine learning and AI which are licensed and commercialized. He received 3 Outstanding Technical Achievement (OTAs), 3 highest Corporate Patent Portfolio awards for contributions in interconnect technologies, holds 68 invention plateaus, and has over 278 US patents covering front end and back end of the line processes and structures, volatile and non-volatile memories, Compute in Memory structures, machine learning algorithms and quantum computing and over 415 international patents. He has authored and co-authored over 220 papers and given over 60 invited/keynote talks and given several Seminars. He received the NY IP Law association “Inventor of the year” award in Feb 2020. He received an industrial pioneer award in 2014 from IEEE Circuits and Systems society. He received the Best Editor Award from the IEEE TVLSI journal. He is inducted into the New Jersey Inventor Hall of Fame in Aug 2014. He won the Mehboob Khan award two times from Semiconductor Research Corporation. He won several best paper awards from ISSCC 1992, ICCAD 2012, ISQED, and VMIC. He is a member of the IBM Academy of technology and a master inventor. He serves on the Board of Governors for IEEE CAS as an industrial liaison. He serves as an IEEE CAS Ambassador to India. He served as a Distinguished Lecturer for IEEE CAS, CEDA, and EDS society. He is an ISQED and World Technology Network fellow and distinguished alumnus of IIT Bombay.

Address:T. J. Watson Research center Yorktown Heights, NY 10598, , Yorktown Heights, New York, United States

Agenda

The event will start at 18:00PM EST and the talk will start at 18:10PM EST.

Media

| IMG_4422 | 2.77 MiB | |

| IMG_4419 | 3.04 MiB | |

| IMG_4417 | 2.57 MiB |