A Novel Simulation Flow for DDR5 Systems with Clocked Receivers

Simulation for DDR5 Systems

A Novel Simulation Flow for DDR5 Systems with Clocked Receivers

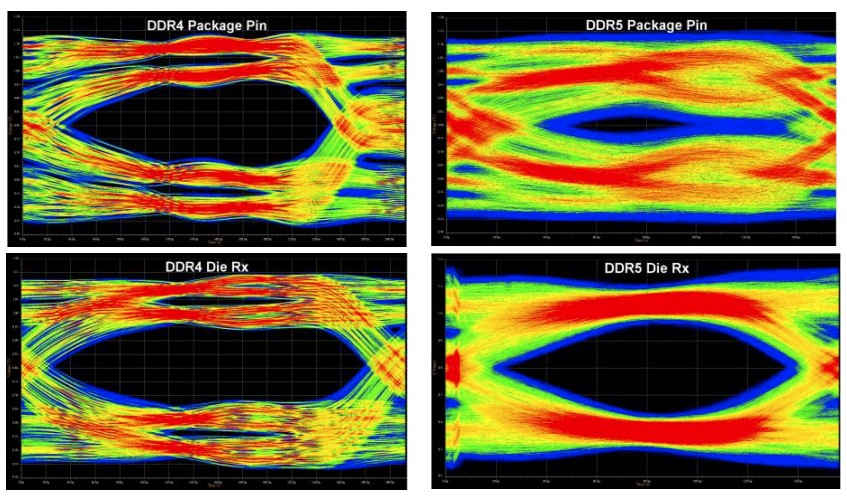

The behavioral simulation needs for DDR5 memory systems have changed significantly since DDR4. The needs for modeling DFE equalization effects with significant clock uncertainty to capture key Signal Integrity effects have added additional complexity to simulation flows. This presentation will address these issues, and the recent enhancements to IBIS and IBIS-AMI, in the context of JEDEC specifications, to make possible accurate and successful DDR5 memory system design.

Matthew Leslie (Siemens EDA)

Justin Butterfield (Micron Technology)

Randy Wolff (Micron Technology)

Hybrid IBIS Summit

Santa Clara, CA

February 3, 2023

Date and Time

Location

Hosts

Registration

-

Add Event to Calendar

Add Event to Calendar

- Contact Event Hosts

-

Lance Wang

Vice Chair, IBIS Open Forum

Lance.Wang@ibis.org - Co-sponsored by IBIS Open Forum

Agenda

Motivations

DDR5 Specification and SI

DDR5 DRAM Device Models

Clocked IBIS-AMI Time-Domain Simulation

Advanced IBIS-AMI Flow

Key Takeaways

Simulation for DDR5 Systems

Media

| Simulation Flow for DDR5 | Simulation Flow for DDR5 | 1.14 MiB |