Thermal Atomic Layer Etch for Logic and Memory Downscaling

#nanotechnology

#memory

#nanoelectronics

#etching

#atomic_layer_etch

#IC_Logic

#thermal_atomic_layer_etch

#ALE

#3D_nanotechnology_architecture

#downscaling

#DRAM

#Logic

#Metals

#Metal_Oxides

#IC_scaling

#IC_Processing

Abstract:

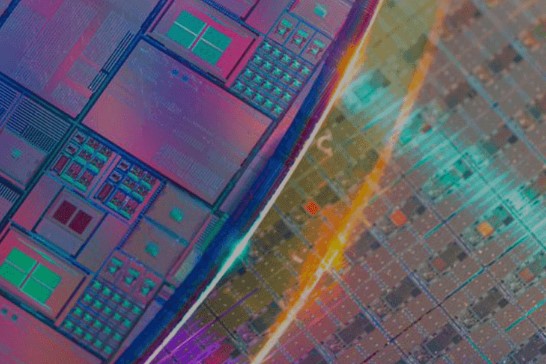

As downscaling approaches physical limits, semiconductor devices are evolving into increasingly complex 3D nano-architectures. Fabricating these unprecedented devices in HVM requires precise and selective material deposition & etch methods.

Atomic layer etch (ALE) helps to sculpt these structures by selectively removing materials with angstrom-scale control. By exploiting chemical differences between materials, ALE processes are designed to etch certain exposed materials while minimizing damage to others. ALE can enable scaling boosters such as fully self-aligned via (FSAV), a critical method for logic back end of line (BEOL) downscaling. Vapor-phase thermal ALE can also provide controlled, selective etch in features with high aspect ratio, low critical dimension, or horizontal openings, overcoming the limitations of wet and plasma etches in emerging 3D structures.

This seminar will focus on ALE of metals and metal oxides for logic and DRAM, including process fundamentals, selectivity mechanisms, and thermal ALE processes developed at EMD Electronics

Bio:

Martin McBriarty

Senior Scientist, EMD Electronics

Martin McBriarty leads atomic layer etch development at EMD Electronics in San Jose, California.

He earned his B.S. in Materials Science & Engineering at the University of Florida in 2008 and his Ph.D. in the same field at Northwestern University in 2014. He studied at the Fritz Haber Institute as a Fulbright scholar and completed postdoctoral work at Pacific Northwest National Laboratory before joining Intermolecular (a business of Merck KGaA, Darmstadt, Germany) in 2018.

In-Person Meeting

Thursday, April 11, 2024

11:30 AM: Networking, Pizza & Drinks

Noon -- 1 pm: Seminar

Please register on Eventbrite before 9:30 AM on Thursday, April 11 , 2024

https://www.eventbrite.com/e/868091132947?aff=oddtdtcreator

Walk-In attendance is welcomed but discouraged

Date and Time

Location

Hosts

Registration

-

Add Event to Calendar

Add Event to Calendar

- EAG Labs

- 810 Kifer Road

- Sunnyvale, California

- United States 95051

- Building: ==> Use corner entrance: Kifer Road / San Lucar Court ==> Do not enter at main entrance on Kifer Road

- Contact Event Host

- Co-sponsored by CH06083 - SCV/SF Jt. Section Chapter, ED15