Third Breakdown : The Discovery and Its Applications in HKMG Generation CMOS and Nonvolatile Memories

There are two major well known breakdowns in CMOS transistor’s history. Not until 2015, a world first observation of the breakdown, different from soft- and hard-breakdown, named dielectric fuse breakdown, dFuse, was discovered, as a milestone when CMOS technology was moved into HKMG era.

In this talk, I will introduce from the inception of the Ig-RTN (Random Telegraph Noise) measurement on the understanding of breakdown in 2008 and briefly describe the fundamentals of RTN technique. Later in 2015, a version 2.0 of this Ig-RTN measurement, named Ig-transient, was successfully developed to delineate the breakdown path in HKMG transistors, from which a third breakdown, named dielectric fuse breakdown, was discovered. Its origin and physical mechanism will be discussed. This breakdown relies on the understanding of a leakage path in the gate dielectric of MOSFET, especially the movement of oxygen ions and the oxygen vacancies in the gate dielectric. In the end, two major applications in memories are presented, one is in the use of One-Time-Programming memory and the other one is on the understanding of the switching phenomena involved in the operation of Resistance Random Access Memory (RRAM).

Date and Time

Location

Hosts

Registration

-

Add Event to Calendar

Add Event to Calendar

Loading virtual attendance info...

- ECE Conference Room

- Department of Electronics & Communication Engineering

- Roorkee, Uttaranchal

- India 247667

Speakers

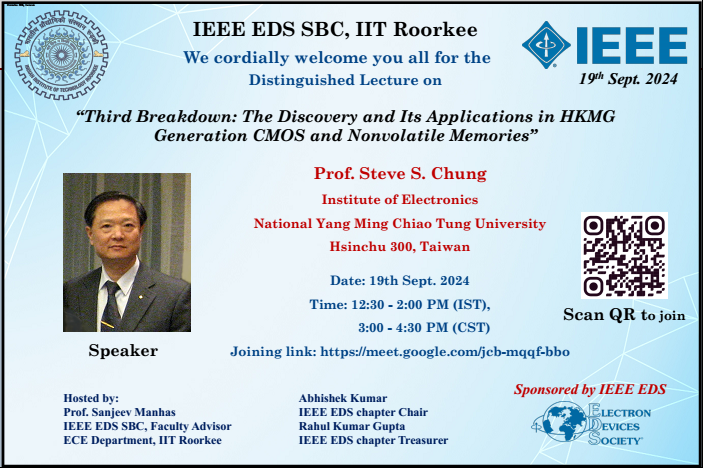

Prof Steve Chung

Third Breakdown : The Discovery and Its Applications in HKMG Generation CMOS and Nonvolatile Memories

Biography:

Prof. Steve Chung received the Ph.D. degree in Electrical Engineering from the University of Illinois at Urbana-Champaign, Champaign, IL, USA. His Ph. D. advisor is the world famous CMOS co-inventor, Prof. C. T. Sah.

Currently, he is NYCU and UMC Chair Professor at the National Yang-Ming Chiao Tung University (NYCU). He has been the Dean of International Affairs Office and Executive Director of school level research center, (2007-2008). He was a visiting professor with Stanford University, University of California-Merced, giving course lectures between 2001-2009 successively. He has been the consultant of two world largest IC foundries, TSMC and UMC. His recent current research areas include- FinFET, flash memory, resistance Memory Technologies, from storage to AI application. He was the first speaker (from Taiwan) to present the paper at VLSI Technology symposium in 1995, in the worldwide leading front of paper presentations in VLSI as corresponding author. He has 35+ times presentations at IEDM/VLSI, more than 300+ publications and also holds about 50 patents.

He is an IEEE Life Fellow, NAI Life Fellow, IEEE Distinguished Lecturer, Senior Editor of Applied Physics-A (Springer), EDS Taipei chapter chair, and with past involvements as IEEE EDS Board of Governor for more than 12 years, EDS Regions/Chapters Chair, and Editor of J-EDS, EDL(2002-2008). Among numerous awards, he has been a recipient of 3-times Outstanding Research Award, Pan Wen Yuan award (2013), Lifetime achievement award as National Inventors (2019) etc.

Email:

Address:Institute of Electronics National Yang Ming Chiao Tung University Hsinchu 300, , Taiwan