IEEE Verilog Coding Competition

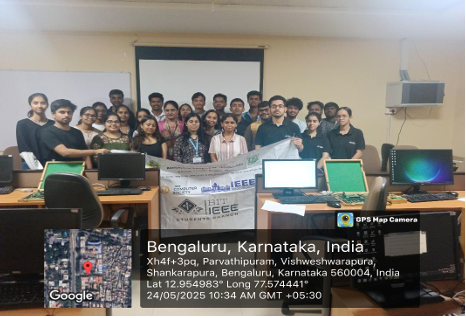

The “Verilogic Showdown” was a dynamic and intellectually stimulating competition conducted on 24th May 2025 at the Department of Electronics and Instrumentation, Bangalore Institute of Technology. The event tested participants' skills in writing efficient Verilog code for real-time hardware problems. Each team’s group lead picked a chit containing a Verilog problem statement. Participants were required to implement the given

task within a fixed time frame using Verilog.

Problem Statements

1. Stepper Motor Control – Rotate 4 steps clockwise and 8 steps anticlockwise.

2. Sine Wave Generation – Write a Verilog program to generate a sine wave.

3. Speed-Controlled Stepper Motor – Rotate at different speeds in opposite directions.

4. Ramp Wave Generation – Generate a ramp wave using Verilog.

5. MOD-8 Counter – Synchronous counter with control signal to count up/down.

6. SIPO Register Implementation – Serial-In Parallel-Out register design in FPGA.

7. Telephone Booth Controller – Coin-based FSM design with test bench and synthesis.

8. Binary to Gray Code Converter – Using 1-bit full adder/subtractor.

9. LED Blinking Pattern – 4 onboard LEDs blinking to simulate clockwise and anticlockwise direction.

10. Vending Machine FSM – Dispense product on receiving 5 rupees from 1/2 rupee coins.

Judging Criteria

The submissions were evaluated based on the following criteria:

• Correctness of Logic

• Efficiency of the Code

• Simulation Output Accuracy

• FSM Implementation (if applicable)

• Bonus Points for Optimization

Date and Time

Location

Hosts

Registration

-

Add Event to Calendar

Add Event to Calendar

- Bangalore Institute Of Technology, Department Of Electronics Engg (VDT)

- Bangalore, Karnataka

- India 560004

- Building: Main building